RTL coding (Verilog/VHDL), CMOS circuit design, EDA tools (Cadence Innovus), timing and power analysis. Design microchips for IoT/automotive, optimize layouts, collaborate with verification teams.

₹33–55 LPA

With 100% Placement Assistance *

Years of Excellence

Years avg exp. of expert faculties

Industry Partners

Active Learners

iHUB DivyaSampark is a Section 8, not-for-profit Technology Innovation Hub at IIT Roorkee, established under the National Mission on Interdisciplinary Cyber-Physical Systems (NM-ICPS) by the Department of Science & Technology (DST), Government of India.

The hub is dedicated to fostering innovation in emerging technologies such as Artificial Intelligence, Machine Learning, Drones, Robotics, and Data Analytics, collectively known as Cyber-Physical Systems (CPS). iHUB aims to become a key enabler of next-generation digital products, services, and solutions across strategic national sectors including healthcare, Industry 4.0, smart cities, and defense.

Coordinated by a high-level inter-ministerial committee chaired by the CEO of NITI Aayog, and senior officials from DST, MeitY, and other ministries, iHUB DivyaSampark works to create an innovation-driven ecosystem by connecting researchers, entrepreneurs, industry, and academia.

In today’s AI era, chip designers have access to AI-powered EDA tools, silicon-proven IP libraries, and open computing platforms like RISC-V Open ISA, enabling them to design powerful, innovative SoCs efficiently. With these advancements, even the most complex SoCs can be realized for next-generation electronic products. However, thorough verification is critical to ensure the success of newly designed chips and systems. This makes it the perfect time for chip designers and VLSI enthusiasts to delve into ASIC verification methodologies and learn how to verify IPs, subsystems, and complete SoCs effectively.

The course covers the complete spectrum of VLSI verification skills, starting with ASIC verification methodologies. It progresses to Advanced Verilog, Code Coverage, SystemVerilog, SystemVerilog Assertions (SVA), followed by Formal Verification, including FPV, formal algorithms, equivalence checking, with detailed case studies.

The course then explores UVM - covering TB architecture, factory, phases, TLM Ports, sequences, virtual sequences and RAL, Gate-Level Simulation (GLS), Timing Verification, SDF annotation, Debugging, regression, low-power verification with UPF, Portable Stimulus Standard (PSS) for test scenario modelling, SoC verification methodology with various case studies. In addition, it also covers Python for DV automation, C programming for writing firmware SoC testcases, and Generative AI for RTL design and verification - empowering engineers with AI-assisted design and verification capabilities

This hands-on course ensures that the participants build strong foundations in Design Verification – functional verification, low-power and formal verification, GLS, DV automation, and SoC verification, while gaining hands-on expertise through labs, case studies, and real-world verification projects.

Curriculum crafted and regularly updated by top semiconductor professionals, aligned with job market needs.

Self-paced and live online classes with Q&A, featuring 70% hands-on learning through labs, mini-projects, and a final capstone project.

Earn an iHUB DivyaSampark,IIT Roorkee certified credential recognized by the semiconductor industry and showcase your verified skills to employers and recruiters worldwide.

Solve real-world challenges with 24/7 lab and EDA tool access, and enhance your portfolio through impactful, project-based learning.

Get exceptional value for your investment with our budget-friendly offerings.

Exclusive masterclasses offering cutting-edge insights, real-world case studies, and advanced techniques to elevate your VLSI and Embedded Systems expertise.

The application process comprises three steps. Candidates are required to submit their application. Selected candidates will receive an offer of admission, which must be confirmed by paying the admission fee.

| # | Start Date | Price | Placement Support | |

|---|---|---|---|---|

| 1 | 28th March | 2,00,000 | Job Assistance | 10 Seats Left |

| # | Course | Duration | Price |

|---|---|---|---|

| 1 | Executive Certification in ASIC Verification With Placement * | 9 Months | ₹2,00,000 + GST |

Price: ₹2,00,000 + GST

Duration: 9 Months

Candidates can pay for the courses through

Share your details to get expert guidance and get eligible for 40% scholarship.

RTL coding (Verilog/VHDL), CMOS circuit design, EDA tools (Cadence Innovus), timing and power analysis. Design microchips for IoT/automotive, optimize layouts, collaborate with verification teams.

₹33–55 LPA

SystemVerilog/UVM, low-power design, floorplanning, clock tree synthesis, DFT (scan insertion). Develop 5G/medical ASICs, implement power-gating, lead physical design integration.

₹33–60 LPA

Place-and-route optimization, DRC/LVS closure, Tcl/Python scripting, 3D-IC packaging. Implement 5nm/3nm node designs, resolve electromigration, GDSII handoff.

₹40–60 LPA

Neural network accelerator design, tensor core optimization, HBM integration, chiplets and wafer-scale engineering. Design AI inference chips, optimize matrix units, implement sparsity-aware architectures.

₹60–85 LPA

ISO 26262 functional safety, automotive Ethernet/IP, thermal simulation, AEC-Q100 qualification. Develop ADAS chips, implement fail-operational systems, EMI/EMC compliance testing.

₹1.2–2.4 Cr

MBIST, scan compression, JTAG/IJTAG protocols, silicon bring-up and debug, yield analysis. Achieve >98% test coverage, develop repair strategies, correlate ATE results.

₹40–60 LPA

* Logos are the trademarks of the respective organizations.

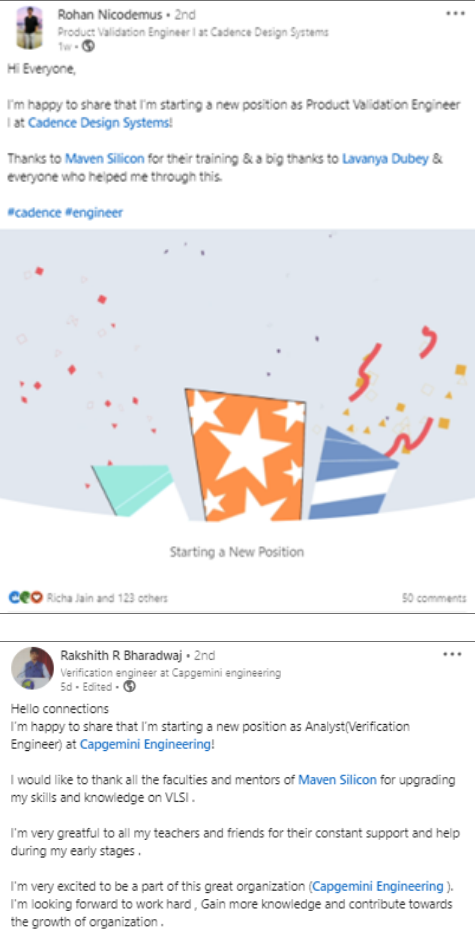

Listen to Our Trainees